# HT9202A/B/C/D/F/G/H/L/S

## 1-Memory/2-Memory Tone/Pulse Dialer

#### Faxback Doc. # 9007546

#### **Features**

- Universal specification

- Operating voltage: 2.0V~5.5V

- Low stand-by current

- Low memory retention current: 0.1μA (Typ.)

- · Tone/pulse switchable

- · Interface with LCD driver

- 32 digits for redialing

- · 32 digits for the SA memory dialing

- · One-key redialing

- Pause and P→T key for PBX

- 4×4 keyboard matrix

- · 3.58MHz crystal or ceramic resonator

- · Hand-free control

- Hold-line control

- Pause, P→T can be saved for redialing

- Lock function for the HT9202L

- Resistor options:

- M/B ratio

- Flash function and flash time

- Pause and P→T duration

Pulse number

- · Memory number:

- HT9202A/B/C/D/S: 2 memories

- HT9202F/G/H/L: 1 memory

### **General Description**

The HT9202 series tone/pulse dialers are CMOS LSIs for the telecommunication system. They are designed to meet various dialing specifications through resistor options matrix.

The HT9202 series tone/pulse dialers are offered in various packages from 16 DIP to 24 SDIP. The 16 DIP version is suitable for low cost applications, while the 24 SDIP version supplies versatile functions such as: Hold-line, Hand-free and LCD dialing number display interface, all of which are suitable for feature phone applications.

The HT9202L provides a long distance call lock for PABX.

#### **Selection Table**

| Function  | Memory<br>No. | Memory<br>Dialing |     |     | LCD<br>Interface | Lock<br>Function | Flash<br>Function | Flash<br>Time<br>(ms) | Pulse<br>No. | Tone<br>Duration<br>(ms) | Inter-<br>Tone-Pause<br>(ms) |      |

|-----------|---------------|-------------------|-----|-----|------------------|------------------|-------------------|-----------------------|--------------|--------------------------|------------------------------|------|

| HT9202A   |               |                   |     |     |                  |                  | Control           | 600                   | N,N+1        | 82.5                     | 85.5                         |      |

| - 18 DIP  | 2             | SA,R              | _   | _   | .   -   -        |                  | Digit             | 600/300/98            | 10-N         | 02.3                     | 65.5                         |      |

| HT9202B   |               |                   | ,   | ,   |                  |                  | Control           | 600                   | N,N+1        | 82.5                     | 85.5                         |      |

| - 22 SDIP | 2             | SA,R              | ٧   | √   | _                |                  | Digit             | 600/300/98            | 10-N         | 02.5                     | \$5.5                        |      |

| HT9202C   | 2             | CAD               |     |     | ,                |                  | Control           | 600                   | N,N+1        | B2.5                     | 85.5                         |      |

| - 20 DIP  | 2             | SA,R              | _ 1 | i — | √                |                  | Digit             | 600/300/98            | 10-N         | 02.0                     | 65.5                         |      |

| HT9202D   |               |                   | 7   | 4   | <b>√</b>         |                  | Control           | 600                   | N,N+1        | N,N+1                    | 82.5                         | 85.5 |

| - 24 SDIP | 2             | SA,R              | N   | l v | \ \ \            | -                | Digit             | 600/300/98            | 10-N         | 02.3                     | 65.5                         |      |

| HT9202F   |               | R                 |     |     |                  |                  | Control           | 600                   | N,N+1        | 82.5                     | 85.5                         |      |

| - 18 DIP  | '             | R                 | _   | _   | _                | _                | Digit             | 600/300/98            | 10-N         | U2.J                     | 05.5                         |      |

| HT9202G   |               | _                 |     |     |                  |                  | Control           | 600                   | N            | 100                      | 106                          |      |

| - 16 DIP  | 1             | R                 | _   | _   | _                | _                | Digit             | 600/300/9B            | 10-N         | 100                      | 100                          |      |

| HT9202H   |               | 5.0               |     |     |                  |                  | Control           | 600                   | N,N+1        | 82.5                     | 85.5                         |      |

| - 18 DIP  | 1             | R/P               | -   | _   | -                | _                | Digit             | 600/300/98            | 10-N         | 02.5                     | 65.5                         |      |

| HT9202L   |               |                   |     |     |                  |                  | Control           | 600                   | N,N+1        | 92.5                     | 85.5                         |      |

| - 18 DIP  | 1 1           | R                 | _   | _   | _                | √                | Digit             | 600/300/98            | 10-N         | 82.5                     | 03.5                         |      |

| HT9202S   |               | 04.0              |     |     |                  |                  | Control           | 600                   | N,N+1        | 82.5                     | 85.5                         |      |

| 20 DIP    | 2             | SA,R              | 4   | -   | _                | -                | Digit             | 600/300/98            | 10-N         | 02.5                     | 03.5                         |      |

8th Feb '96

1

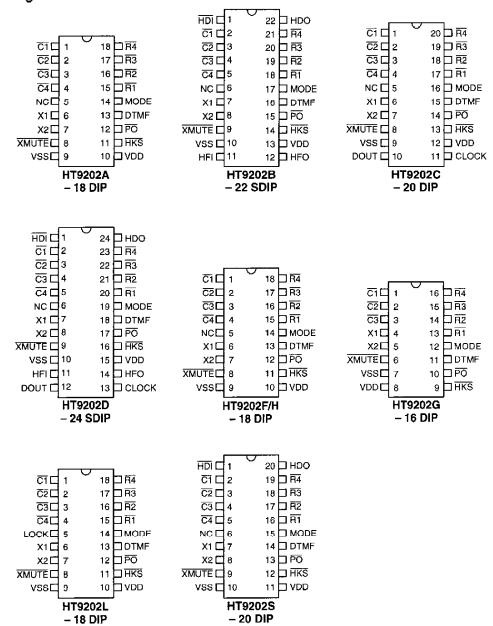

#### **Package Information**

2

8th Feb '96

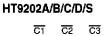

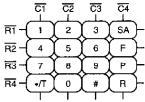

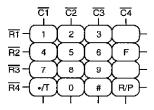

## **Keyboard Information**

Note: HT9202F/L:  $\overline{C4} = \overline{C4}$ HT9202G: C4 = HKS

#### HT9202F/G/L

HT9202H

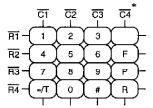

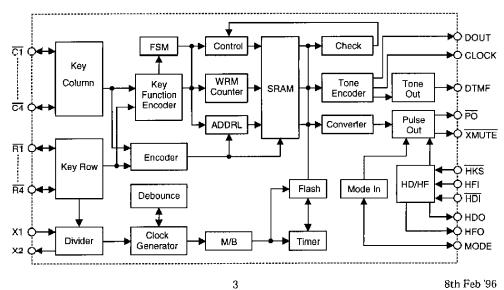

## **Block Diagram**

#### HT9202A/B/C/D/S

8th Feb '96

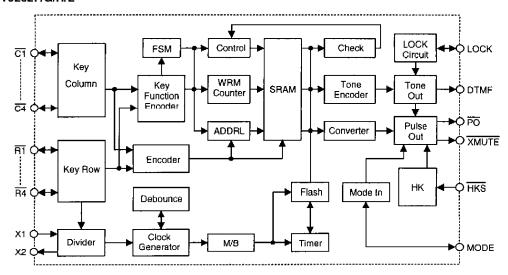

#### HT9202F/G/H/L

## **Pin Description**

| Pin Name                       | I/O | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>C1</u> - <u>C4</u><br>R1~R4 | I/O | CMOS<br>IN/OUT         | These pins construct a 4×4 keyboard matrix to perform the keyboard input detecting and dialing specification setting functions. When on-hook ( $\overline{HKS}$ =high) all the pins are set to high. While off-hook the column group ( $\overline{C1}\sim\overline{C4}$ ) stays low and the row group ( $\overline{R1}\sim\overline{R4}$ ) is set to high for key input detecting. An inexpensive single contact 4×4 keyboard can be used as an input device. Pressing a key connects a single column to a single row, and actuates the system oscillator to result in a dialing signal output. If more than two keys are pressed at the same time, no response can be brought about. The key-in debounce time is 20ms. Refer to the keyboard table for keyboard arrangement and to the functional description for dialing specification selection. |

| X1                             | 1   | OSCILLATOR             | The system oscillator consists of an inverter, a bias resistor and the necessary load capacitor on chip. Connecting a standard 3.579545MHz crystal or ceramic resonator to X1 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| X2                             | О   | OSOILLATOR             | X2 terminals can implement the oscillator function. The oscillator is turned off in the stand-by mode, and is actuated whenever a keyboard entry is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XMUTE                          | 0   | NMOS OUT               | The XMUTE is an NMOS open drain structure pulled to VSS during dialing signal transmitting. Otherwise, it is an open circuit. The XMUTE is used to mute the speech circuit when transmitting the dial signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin Name | I/O | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-----|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| НKS      | I   | CMOS IN                | This pin is used to monitor the status of the hook-switch and its combination with HFI can control the PO pin output to make or break the line.  HKS=VDD: On-hook state (PO=low). Except HFI/HDI (hand-free/hold-line control input), other functions are all disabled.  HKS=VSS: Off-hook state (PO=high). The chip is in the stand-by mode and ready to receive the key input.                                                                                                                                                                     |

| PO       | 0   | CMOS OUT               | This pin is a CMOS output structure which receives $\overline{HKS}$ and HFO signals to control the dialer so as to connect or disconnect the telephone line. $\overline{PO}$ outputs low to break line when $\overline{HKS}$ is high (on-hook) and HFO is low (hand-free inactive). $\overline{PO}$ outputs high to make line when $\overline{HKS}$ is low (off-hook) or HFO is high or HDO is high. During the off-hook state, the pin also outputs the dialing pulse train in pulse mode dialing. While in the tone mode, this pin is always high. |

| MODE     | I/O | CMOS<br>IN/OUT         | This is a three-state input/output pin, provided to the user for selecting a dialing mode among Tone/20pps/10pps.  MODE=VDD: Pulse mode, 10pps.  MODE=OPEN: Pulse mode, 20pps.  MODE=VSS: Tone mode.  During the pulse mode dialing, switching this pin to the tone mode changes the following entrance of digits to the tone mode. When the chips are working in the tone mode, the switching from tone to the pulse mode will be recognized.                                                                                                       |

| DTMF     | 0   | CMOS OUT               | This pin is active only when the chip transmits tone dialing signals. Otherwise, it always outputs low. The pin outputs tone signals to drive the external transmitter amplifier circuit. The load resistor should not be less than $5K\Omega$ .                                                                                                                                                                                                                                                                                                     |

| ĦDI      | I   | CMOS IN<br>Pull-High   | This pin is a schmitt trigger input structure. Active low. Applying a negative going pulse to this pin can toggle the HDO output once. An external RC network is recommanded to use for the input debouncing. The pull-high resistance is $200 \mathrm{K}\Omega$ typically.                                                                                                                                                                                                                                                                          |

| HDO      | 0   | CMOS OUT               | The HDO is a CMOS output structure. Its output is toggle-controlled by a negative transition on $\overline{HDI}$ . When HDO is toggled to high, $\overline{PO}$ keeps high to hold the line. The hold function can be released by setting HFO high or by an on-off hook operation or by another $\overline{HDI}$ input. The HDO pin can directly drive the HT3810 series melody generator to produce hold-line back ground melody. Refer to the functional description for the hold-line function.                                                   |

5

| Pin Name | I/O | Internal<br>Connection | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HFI      | I   | CMOS IN<br>Pull-Low    | This pin is a schmitt trigger input structure. Active high. Applying a positive going pulse to HFI can toggle the HFO once and hence control the hand-free function. The pull-low resistance of HFI is $200 \mathrm{K}\Omega$ typically. An external RC network is recommanded to use for the input debouncing.                                                                                       |

| HFO      | 0   | CMOS OUT               | The HFO is a CMOS output structure. Its output is toggle-controlled by a positive transition on HFI pin. When HFO is high, the hand-free function is enabled and PO outputs high to connect the line.  The hand-free function can be released by setting HDO high or by an on-off-hook operation or by another HFI input. Refer to the functional description for the hand-free functional operation. |

| LOCK     | I/O | CMOS IN/OUT            | This is a three-state input/output pin, provided to the user for controlling the long distance call function with a lock-switch. LOCK=VDD: Normal dialing. LOCK=OPEN: "0, 9" is inhibited for use as the first key input. LOCK=VSS: "0" is inhibited for use as the first key input.                                                                                                                  |

| DOUT     | 0   | NMOS OUT               | This is an NMOS open drain output pin. It outputs the BCD code of the dialing digits to the LCD driver chip (HT16XX series) or $\mu C$ for dialing number display. Refer to the functional description for the detailed timing.                                                                                                                                                                       |

| CLOCK    | 0   | NMOS OUT               | NMOS open drain output. When dialing, it outputs a series of pulse trains for the DOUT data synchronization. The DOUT data is valid at the falling edge of clock.                                                                                                                                                                                                                                     |

| VDD      | I   |                        | Positive power supply, 2.0V~5.5V for normal operation.                                                                                                                                                                                                                                                                                                                                                |

| VSS      | I   | _                      | Negative power supply                                                                                                                                                                                                                                                                                                                                                                                 |

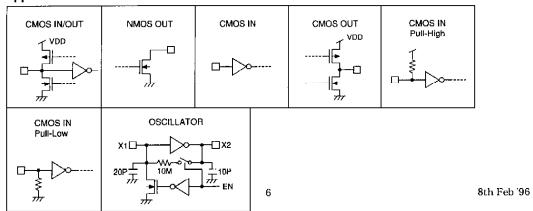

## Approximate Internal connection circuits

## **Absolute Maximum Ratings**

Supply Voltage ....... -0.3V to 6V Input Voltage ......  $V_{SS}-0.3$  to  $V_{DD}+0.3V$  Storage Temperature ......  $-50^{\circ}$ C to  $125^{\circ}$ C Operating Temperature .......  $-20^{\circ}$ C to  $75^{\circ}$ C

## **Electrical Characteristics**

(F<sub>OSC</sub>=3.5795MHz, Ta=25°C)

|                  | ectrical Orial acteristics          |                |                         |                         |                      |        | (FOSC=5.5795MHz, Ta=25°C |      |  |  |  |

|------------------|-------------------------------------|----------------|-------------------------|-------------------------|----------------------|--------|--------------------------|------|--|--|--|

| C1               | D                                   | Test Condition |                         |                         | 3.51                 | _      | Max.                     |      |  |  |  |

| Symbol           | Parameter                           | $V_{DD}$       | С                       | ondition                | Min.                 | Тур.   | Max.                     | Unit |  |  |  |

| $V_{DD}$         | Operating Voltage                   | _              |                         | _                       | 2                    |        | 5.5                      | V    |  |  |  |

|                  |                                     |                | Pulse                   | Off-hook                |                      | 0.2    | 1                        | mA   |  |  |  |

| $I_{DD}$         | Operating Current                   | 2.5V           | Tone                    | Keypad entry<br>No load | _                    | 0.6    | 2                        | mA   |  |  |  |

| I <sub>STB</sub> | Stand-by Current                    | 1V             | On-ho<br>No ent         | ok, no load<br>try      |                      |        | 1                        | μА   |  |  |  |

| VR               | Memory Retention Voltage            | _              |                         | -                       | 1                    | _      | 5.5                      | V    |  |  |  |

| $I_R$            | Memory Retention Current            | 1V             | On-ho                   | ok                      | _                    | 0.1    | 0.2                      | μA   |  |  |  |

| VIL              | Input Low Voltage                   | _              |                         | _                       | Vss                  | _      | $0.2V_{\mathrm{DD}}$     | V    |  |  |  |

| VIH              | Input High Voltage                  | _              |                         |                         | $0.8V_{\mathrm{DD}}$ | _      | $V_{\mathrm{DD}}$        | V    |  |  |  |

| I <sub>XMO</sub> | XMUTE Leakage Current               | _              | Vxmui<br>No ent         | TE=12V<br>try           | _                    | _      | 1                        | μА   |  |  |  |

| IOLXM            | XMUTE Sink Current                  | 2.5V           | VXMUT                   | E=0.5V                  | 1                    | _      | _                        | mA   |  |  |  |

| I <del>HKS</del> | HKS Pin Input Current               | 2.5V           | V <del>HKS</del> =      | 2.5V                    | _                    | _      | 0.1                      | μA   |  |  |  |

| R <sub>HFI</sub> | HFI Pull-Low Resistance             | 2.5V           | V <sub>HFI</sub> =      | 2.5V                    | _                    | 200    |                          | ΚΩ   |  |  |  |

| RHDI             | HDI Pull-High Resistance            | 2.5V           | 5V V <sub>HDI</sub> =0V |                         |                      | 200    |                          | ΚΩ   |  |  |  |

| Іон1             | Keypad Pin Source Current           | 2.5V           | Von=0                   | )V                      | -4                   | _      | -40                      | μΑ   |  |  |  |

| Ioli             | Keypad Pin Sink Current             | 2.5V           | V <sub>OL</sub> =2      | .5V                     | 200                  | 400    |                          | μΑ   |  |  |  |

| Іон2             | HFO Pin Source Current              | 2.5V           | V <sub>OH</sub> =2      | ev                      | -1                   |        | _                        | mΑ   |  |  |  |

| I <sub>OL2</sub> | HFO Pin Sink Current                | 2.5V           | V <sub>OL</sub> =0      | .5V                     | 1                    | _      | L – 1                    | mΑ   |  |  |  |

| Іонз             | HDO Pin Source Current              | 2.5V           | V <sub>OH</sub> =2      | .V                      | -1                   |        |                          | mA   |  |  |  |

| I <sub>OL3</sub> | HDO Pin Sink Current                | 2.5V           | V <sub>OL</sub> =0      | .5V                     | 1                    | -      |                          | mΑ   |  |  |  |

| Тғр              | Pause Time After Flash              |                | Contro                  | ol key                  |                      | 0.2    |                          | s    |  |  |  |

| 144              | 1 ause Time Arter Flash             |                | Digit k                 | ey                      |                      | I      | _                        |      |  |  |  |

| T <sub>RP</sub>  | Onc-key Redialing Pause<br>Time     |                | One-key redialing       |                         | _                    | 1      | _                        | s    |  |  |  |

| T <sub>DB</sub>  | Key-in Debounce Time                |                | _                       |                         | _                    | 20     | -                        | ms   |  |  |  |

| T <sub>BRK</sub> | Break Time for One-key<br>Redialing |                | One-ke                  | ey redialing            |                      | 2      | _                        | s    |  |  |  |

| Fosc             | System Frequency                    | _              | Crysta                  | l=3.5795MHz             | 3.5759               | 3.5795 | 3.5831                   | MH2  |  |  |  |

## **Pulse Mode Electrical Characteristics**

(F<sub>OSC</sub>=3.5795MHz, Ta=25°C)

| Symbol           | Damamatar                   |                           | Test Condition                                                      | Min  | Tues                     | Mor  | T7 *4 |  |

|------------------|-----------------------------|---------------------------|---------------------------------------------------------------------|------|--------------------------|------|-------|--|

| Symbol           | Parameter                   | V <sub>DD</sub> Condition |                                                                     | Min. | Тур.                     | Max. | Unit  |  |

| I <sub>POH</sub> | PO Output Source<br>Current | 2.5V                      | V <sub>OH</sub> =2V                                                 | -0.2 |                          | _    | mA    |  |

| I <sub>POL</sub> | PO Output Sink<br>Current   | 2.5V                      | V <sub>OL</sub> =0.5V                                               | 0.2  | 0.6                      | _    | mA    |  |

| DD               | Pulse Rate                  |                           | MODE pin is connected to V <sub>DD</sub> .                          | _    | 10                       |      | pps   |  |

| PR               | Pulse Rate                  |                           | MODE pin is opened.                                                 |      | 20                       | _    |       |  |

| M/B              | Mala Danis Dani             |                           | A resistor is linked between R2 and C1.                             | _    | 33:66                    | _    | %     |  |

|                  | Make/Break Ratio            |                           | No resistor is linked between R2 and C1.                            |      | 40:60                    | _    |       |  |

|                  |                             |                           | M/B ratio=40:60                                                     | _    | 40 (10pps)<br>20 (20pps) |      |       |  |

| T <sub>PDP</sub> | Prc-digit-pause Time        | -                         | M/B ratio=33:66                                                     | _    | 33 (10pps)<br>17 (20pps) | _    | ms    |  |

|                  | T                           |                           | Pulse rate=10pps                                                    | _    | 800                      |      |       |  |

| $T_{IDP}$        | Inter-digit-pause Time      | _                         | Pulse rate=20pps                                                    |      | 500                      | _    | ms    |  |

| <b>T</b>         |                             |                           | A resistor is linked between R2 and C1.                             | _    | 33 (10pps)<br>17 (20pps) |      | ms    |  |

| T <sub>M</sub>   | Pulse Make Duration         |                           | No resistor is linked between $\overline{R2}$ and $\overline{C1}$ . | _    | 40 (10pps)<br>20 (20pps) | _    |       |  |

| Тв               | D.1. D. 1.D                 |                           | A resistor is linked between R2 and C1.                             | _    |                          |      |       |  |

|                  | Pulse Break Duration        | _                         | No resistor is linked between R2 and C1.                            | _    | 60 (10pps)<br>30 (20pps) | _    | ms    |  |

## **Tone Mode Electrical Characteristics**

$(F_{OSC}=3.5795MHz, Ta=25^{\circ}C)$

|                  |                      |                 | Test Condition                 |                       | Тур.  | Max.                 | Unit   |

|------------------|----------------------|-----------------|--------------------------------|-----------------------|-------|----------------------|--------|

| Symbol           | Parameter            | V <sub>DD</sub> | Condition                      | Min.                  |       |                      |        |

| V <sub>TDC</sub> | DTMF Output DC Level | _               | _                              | $0.45V_{\mathrm{DD}}$ | _     | $0.7V_{\mathrm{DD}}$ | V      |

| ITOL             | DTMF Sink Current    | 2.5V            | V <sub>DTMF</sub> =0.5V        | 0.1                   | _     | _                    | mA     |

| VTAC             | DTMF Output AC Level | _               | Row group, R <sub>L</sub> =5KΩ | 0.12                  | 0.155 | 0.18                 | Vr.m.s |

| Sambal                             | Parameter                   |                 | Test C                | ondition                  | Min. | т    | Max.         | Unit |

|------------------------------------|-----------------------------|-----------------|-----------------------|---------------------------|------|------|--------------|------|

| Symbol                             | Farameter                   | V <sub>DD</sub> | C                     | Condition                 |      | Тур. |              |      |

| RL                                 | DTMF Output Load            | 2.5V            | THD≤-                 | -23dB                     | 5    | _    | _            | ΚΩ   |

| Acr                                | Column Pre-emphasis         | 2.5V            | 2.5V Row group=0dB    |                           | 1    | 2    | 3            | dB   |

| THD                                | Tone Signal Distortion      | 2.5V            | V R <sub>L</sub> =5KΩ |                           | _    | -30  | -23          | dB   |

|                                    |                             |                 | Auto-                 | HT9202A/B/C/<br>D/F/H/L/S | _    | 82.5 | _            | ms   |

| T <sub>TMIN</sub> Minimum Tone Dur | Minimum I one Duration      | _               | redial                | HT9202G                   | _    | 100  |              | ms   |

| TTDM                               | Minimum Inter-tone<br>Pausc | _               | Auto-<br>redial       | HT9202A/B/C/<br>D/F/H/L/S | _    | 85.5 | _            | ms   |

|                                    |                             |                 |                       | HT9202G                   | _    | 106  | <del>-</del> | ms   |

THD (Distortion) (dB) = 20 log (  $\sqrt{V1^2 + V2^2 + ... + Vn^2} / \sqrt{Vi^2 + Vh^2}$  )

Vi, Vh: Row group and column group signals

V1, V2, ... Vn: Harmonic signals (BW=300Hz~3500Hz)

## **Functional Description**

## **Keyboard matrix**

The  $\overline{\text{C1}} \sim \overline{\text{C4}}$  and  $\overline{\text{R1}} \sim \overline{\text{R4}}$  make up of a keyboard matrix. Together with a standard 4×4 keyboard, the keyboard matrix is used for dialing entrance. In addition, the keyboard matrix provides resistor option for different dialing specification selections. The keyboard arrangement for each of the HT9202 series are listed in **Keyboard Information**.

#### Tone frequency

| T NI      | Output Freq | % Error |         |

|-----------|-------------|---------|---------|

| Tone Name | Specified   | Actual  | % Error |

| R1        | 697         | 699     | +0.29%  |

| R2        | 770         | 766     | -0.52%  |

| R3        | 852         | 847     | -0.59%  |

| R4        | 941         | 948     | +0.74%  |

| C1        | 1209        | 1215    | +0.50%  |

| C2        | 1336        | 1332    | -0.30%  |

| C3        | 1477        | 1472    | -0.34%  |

<sup>%</sup> Error does not contain the crystal frequency drift.