|  | D |

|--|---|

# **POWERTIPTECH.CORP.**

ISPLAY DEVICES FOR BETTER ELECTRONIC DESIGN

| Specification For Approval |                                |  |                                              |            |  |  |  |

|----------------------------|--------------------------------|--|----------------------------------------------|------------|--|--|--|

| Customer                   | :                              |  |                                              |            |  |  |  |

| Model Type                 | Model Type : <u>LCD Module</u> |  |                                              |            |  |  |  |

| Sample Code                | :                              |  | PG12864LRS-KNN-H-S0                          |            |  |  |  |

| Mass Produ                 | uction Code :                  |  |                                              |            |  |  |  |

| Edition                    | :                              |  | <u>    0                                </u> |            |  |  |  |

|                            |                                |  |                                              |            |  |  |  |

| CustomerSign               | SalesSign                      |  | ApprovedBy                                   | PreparedBy |  |  |  |

PT-R-003-3

## CONTENTS

## **1.SPECIFICATIONS**

- 1.1 Features

- 1.2 Mechanical Specifications

- 1.3 Absolute Maximum Ratings

- 1.4 DC Electrical Characteristics

- 1.5 Optical Characteristics

- 1.6 Backlight Characteristics

## **2.MODULE STRUCTURE**

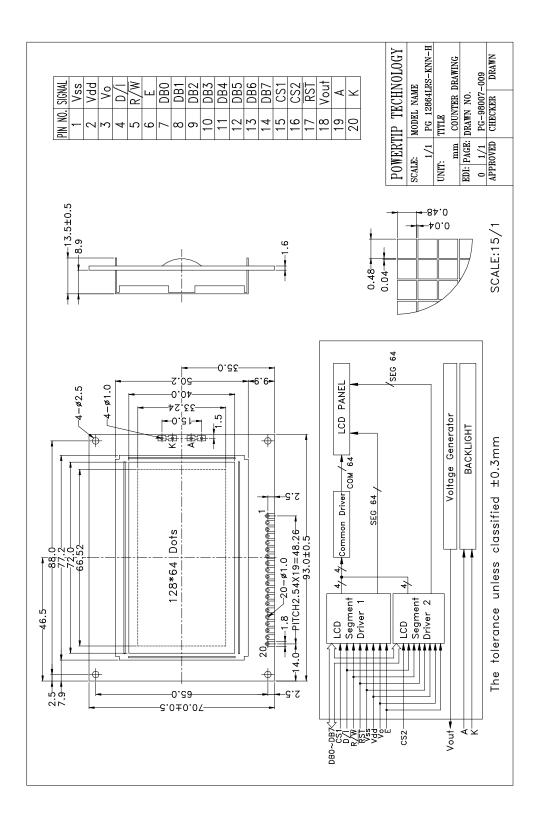

- 2.1 Counter Drawing

- 2.2 Interface Pin Description

- 2.3 Timing Characteristics

- 2.4 Display Command

#### **1. SPECIFICATIONS**

#### **1.1 Features**

- $\iota\,$  Full dot-matrix structure with 128 dots \*64 dots

- ι 1/64 Duty, 1/9 bias

- ι STN LCD, positive

- ι Transflective LCD, gray display

- ι 6 o'clock viewing angle

- ι 8 bits parallel data input.

- $\iota\,$  Built-in negative voltage and LED backlight

## **1.2 Mechanical Specifications**

- ι Outline dimension : 93.0mm(L) \*70.0mm(W)\*14.0mm max.(H)

- ι Viewing area : 72.0mm\*40.0mm

- ۱ Active area : 66.52mm\*33.24mm

- ι Dot size : 0.48mm\*0.48mm

- ι Dot pitch : 0.52mm\*0.52mm

#### **1.3 Absolute Maximum Ratings**

| Item                     | Symbol  | Conditions | Min. | Max.    | Unit |

|--------------------------|---------|------------|------|---------|------|

| Power supply Voltage     | VDD     | -          | 4.5  | 5.5     | V    |

| LCD drive Supply voltage | VDD-VEE | -          | 8.0  | 17      | V    |

| Input voltage            | VIN     | -          | -0.3 | VDD+0.3 | V    |

| Operating temperature    | TOPR    | -          | -20  | 70      | °C   |

| Storage temperature      | TSTG    | -          | -30  | 80      | °C   |

| Humidity                 | Hd      | -          | -    | 90      | %RH  |

#### **1.4 DC Electrical Characteristics**

VDD=+5V<u>+</u>10%,VSS=0V,TA=25°C

| Item                 | Symbol | Condition | Min.    | Тур.  | Max.   | Unit |

|----------------------|--------|-----------|---------|-------|--------|------|

| Logic Supply voltage | Vdd    | -         | 4.5     | 5     | 5.5    | V    |

| "H" input voltage    | VIH    | -         | 0.7Vdd  | -     | VDD    | V    |

| "L" input voltage    | VIL    | -         | 0       | I     | 0.3VDD | V    |

| "H" output voltage   | Vон    | -         | VDD-0.4 | I     | -      | V    |

| "L" output voltage   | Vol    | -         | -       | I     | 0.4    | V    |

| Supply current       | IDD    | VDD=5V    | -       | 7.88  | 9.73   | mA   |

| LCD driving voltage  | VOP    | VDD-VO    | -       | 12.55 | 14.45  | V    |

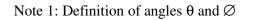

## **1.5 Optical Characteristics**

| 1/64 duty, 1/9 bias, V |    | V <sub>OPR</sub> =13.6V, Ta=25°C |  |  |  |

|------------------------|----|----------------------------------|--|--|--|

| m                      | 14 | D C                              |  |  |  |

| Item                | Symbol           | Conditions | Min. | Тур.  | Max   | Reference   |

|---------------------|------------------|------------|------|-------|-------|-------------|

| Viewing angle       | θ                | C≥2.0,Ø=0° | 30°  | -     | -     | Notes 1 & 2 |

| Contrast            | С                | θ=5°, Ø=0° | -    | 3     | -     | Note 3      |

| Response time(rise) | $T_r$            | θ=5°, Ø=0° | -    | 140ms | 200ms | Note 4      |

| Response time(fall) | $T_{\mathrm{f}}$ | θ=5°, Ø=0° | -    | 300ms | 500ms | Note 4      |

| Demonstern         | Course la sel   |                  |      | Standard |      |      |  |

|--------------------|-----------------|------------------|------|----------|------|------|--|

| Parameter          | Symbol          | Temperature (°C) | Min  | Тур      | Max  | Unit |  |

|                    | -20             | 14.3             | 14.7 | 15.1     |      |      |  |

| Driving<br>voltage | V <sub>OP</sub> | 25               | 13.2 | 13.6     | 14.0 | V    |  |

|                    |                 | 70               | 12.0 | 12.4     | 12.8 |      |  |

Note 2: Definition of viewing angles  $\theta 1$  and  $\theta 2$

## **1.6 Backlight Characteristic**

The LCD Module is using a LED backlight •.Maximum Ratings

| Item                  | Symbol | Conditions | Min. | Max. | Unit |

|-----------------------|--------|------------|------|------|------|

| Forward current       | IF     | TA=25°C    | -    | 975  | mA   |

| Reverse voltage       | VR     | TA=25°C    | -    | 8    | V    |

| Power dissipation     | Ро     | TA=25°C    | -    | 4.5  | W    |

| Operating Temperature | TOPR   | -          | -20  | 70   | °C   |

| Storage temperature   | TSTG   | -          | -40  | 80   | °C   |

•.Electrical Ratings

|                                     | TA=25°C      |           |      |      |      |                   |  |

|-------------------------------------|--------------|-----------|------|------|------|-------------------|--|

| Item                                | Symbol       | Condition | Min. | Тур. | Max. | Unit              |  |

| Forward voltage                     | VF           | IF=390mA  |      | 4.2  | 4.6  | V                 |  |

| Reverse current                     | IR           | VR=8V     | -    | -    | 0.2  | mA                |  |

| Luminous intensity<br>(without LCD) | IV           | IF=390mA  | 184  | 230  | -    | cd/m <sup>2</sup> |  |

| Luminous intensity<br>(with LCD)    | IV           | IF=390mA  | -    | 84.1 | -    | cd/m <sup>2</sup> |  |

| Wavelength                          | λp           | IF=390mA  | 571  | -    | 576  | nm                |  |

| Color                               | Yellow Green |           |      |      |      |                   |  |

## 2. MODULE STRUCTURE

#### **2.1 Counter Drawing**

\*See Appendix 1

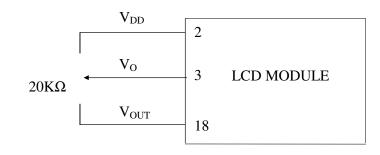

## 2.2 Interface Pin Description

| Pin No. | Symbol           | Function                                                                                                                         |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>SS</sub>  | Power Supply (Vss=0)                                                                                                             |

| 2       | $V_{DD}$         | Power Supply (V <sub>DD</sub> >V <sub>SS</sub> )                                                                                 |

| 3       | Vo               | Operating voltage for LCD                                                                                                        |

| 4       | D/ I             | Register selection input<br>High =Data register<br>Low =Instruction register (for write)<br>Busy flag address counter (for read) |

| 5       | R/W              | R/W signal input is used to select the read/write mode<br>High =Read mode, Low =Write mode                                       |

| 6       | Е                | Start enable signal to read or write the data                                                                                    |

| 7-14    | DB0~DB7          | Data bus line                                                                                                                    |

| 15      | CS1              | Chip enable for D2 (segment 1 to segment 64)                                                                                     |

| 16      | CS2              | Chip enable for D3 (segment 65 to segment 128)                                                                                   |

| 17      | RST              | Reset signal                                                                                                                     |

| 18      | V <sub>OUT</sub> | Negative voltage supply                                                                                                          |

| 19      | А                | Power supply for LED backlight (+)                                                                                               |

| 20      | K                | Power supply for LED backlight (- )                                                                                              |

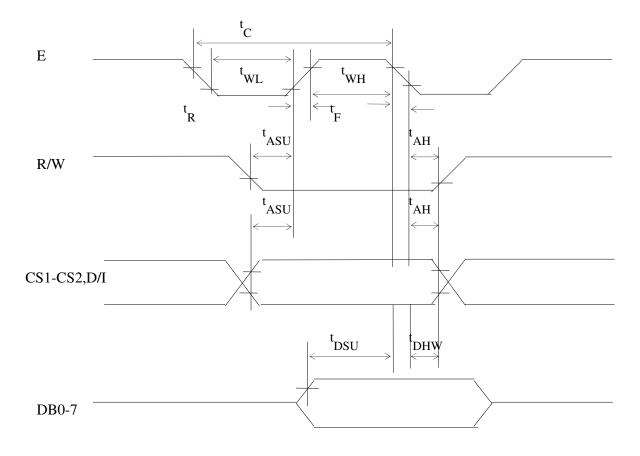

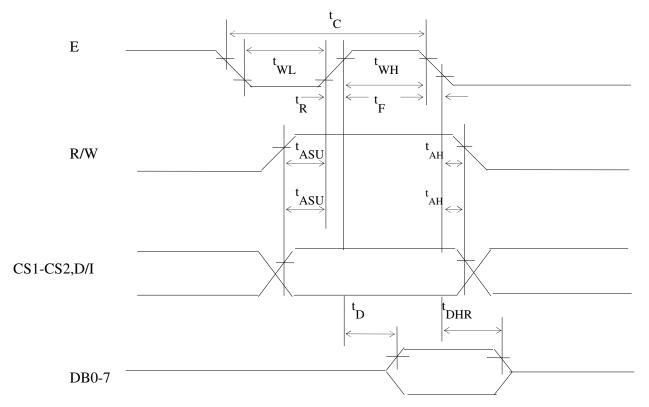

## 2.3 Timing Characteristics

MPU write timing

MPU read timing

| Characteristic         | Symbol           | Min. | Тур | Max | Unit |

|------------------------|------------------|------|-----|-----|------|

| E Cycle                | t <sub>C</sub>   | 1000 | -   | -   | ns   |

| E High Level Width     | t <sub>WH</sub>  | 450  | -   | -   | ns   |

| E Low Level Width      | $t_{\rm WL}$     | 450  | -   | -   | ns   |

| E Rise Time            | t <sub>R</sub>   | -    | -   | 25  | ns   |

| E Fall Time            | t <sub>F</sub>   | -    | -   | 25  | ns   |

| Address Set-Up time    | t <sub>ASU</sub> | 140  | -   | -   | ns   |

| Address Hold Time      | t <sub>AH</sub>  | 10   | -   | -   | ns   |

| Data Set-Up Time       | t <sub>SU</sub>  | 200  |     | -   | ns   |

| Data Delay Time        | t <sub>D</sub>   | -    | -   | 320 | ns   |

| Data Hold Time (Write) | t <sub>DHW</sub> | 10   | -   | -   | ns   |

| Data Hold Time (Read)  | t <sub>DHR</sub> | 20   | -   | -   | ns   |

## 2.4 Display command

|                      |    |     |       |       | Co    | de    |       | -    |       |      |                                                   |  |  |  |  |

|----------------------|----|-----|-------|-------|-------|-------|-------|------|-------|------|---------------------------------------------------|--|--|--|--|

|                      | R/ | D/I | DB7   | DB    | DB5   | DB    | DB    | DB   | DB    | DB(  | D                                                 |  |  |  |  |

| Instructions         | W  |     |       | 6     |       | 4     | 3     | 2    | 1     |      | Functions                                         |  |  |  |  |

| Display on/off       | 0  | 0   | 0     | 0     | 1     | 1     | 1     | 1    | 1     | 1/0  | Controls display on/off. RAM data and interna     |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | status are not affected.                          |  |  |  |  |

| Display start line   | 0  | 0   | 1     | 1     | Displ | ay s  | tart  | line | (0-6  | (3   | Specifies the RAM line displayed at the top of th |  |  |  |  |

|                      |    |     |       |       |       | 1     |       |      |       |      | screen.                                           |  |  |  |  |

| Set Page (x address) | 0  | 0   | 1     | 0     | 1     | 1     | 1     | Pag  | ge (( | )-7) | Sets the page (X address) of RAM at the page(     |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | address) register.                                |  |  |  |  |

| Set Y address        | 0  | 0   | 0     | 1     | Y add | iress | s (0- | 63)  | 'n    |      | Sets the Y address in the counter.                |  |  |  |  |

| Status read          | 1  | 0   | Busy  | 0     | ON/   | Res   | et 0  | 0    | 0     | 0    | Reads the status.                                 |  |  |  |  |

|                      |    |     |       |       | OFF   |       |       |      |       |      | Reads1: Reset                                     |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | 0: Normal                                         |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | ON/OFF1: Display off                              |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | 0: Display on                                     |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | Busy1: Internal operation                         |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | 0: Ready                                          |  |  |  |  |

| Write display data   | 0  | 1   | Write | e da  | ta    |       |       |      |       |      | Writes data DB0 (LSB) to Has access to the        |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | DB7(MSB)onthedatabus address of the               |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | into display displayRAM                           |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | RAM. specified in                                 |  |  |  |  |

| Read display data    | 1  | 1   | Read  | l dat | a     |       |       |      |       |      | Reads data DB0 (LSB) advance. After the           |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | to DB7 (MSB) from the access, Y address i         |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | display RAM to the data increased by 1.           |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      | bus.                                              |  |  |  |  |

|                      |    |     |       |       |       |       |       |      |       |      |                                                   |  |  |  |  |

## **Detailed Explanation**

#### **Display On/Off**

| R/W D/IDB7 |   |   |   |   | I | DB0 |   |   |   |   |

|------------|---|---|---|---|---|-----|---|---|---|---|

| Code       | 0 | 0 | 0 | 0 | 1 | 1   | 1 | 1 | 1 | D |

#### **MSBLSB**

The display data appears when D is 1 and disappears when D is 0. Though the data is not on the screen with D=0, it remains in the display data RAM. Therefore, you can make it appear by changing D=0 into D=1.

| Display St    | tart L   | ine    |        |          |         |        |         |        |          |         |               |

|---------------|----------|--------|--------|----------|---------|--------|---------|--------|----------|---------|---------------|

| R/W D/IDB7    |          |        |        |          | I       | OB0    |         |        |          |         | _             |

| Code          | 0        | 0      | 1      | 1        | А       | А      | А       | А      | А        | А       |               |

| MSBLSB        |          |        |        |          |         |        |         |        |          |         |               |

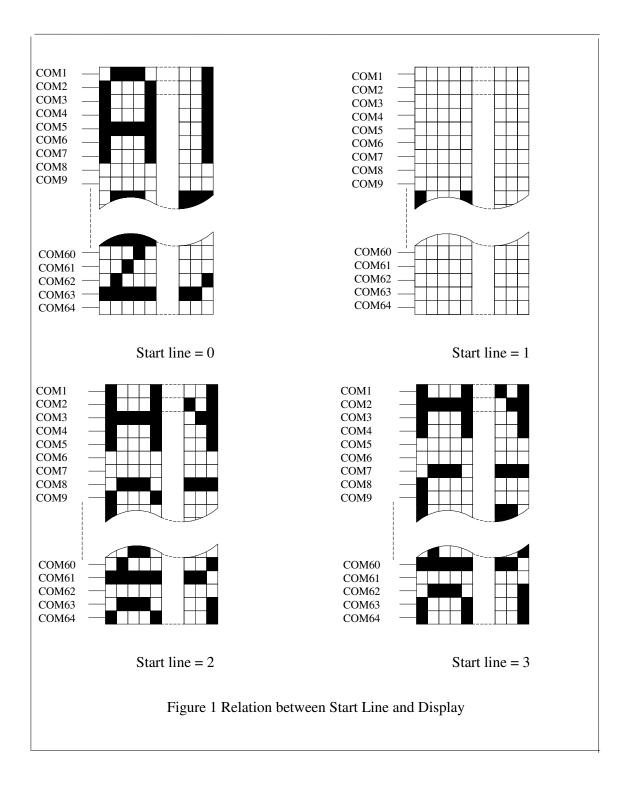

| Z address A   | AAAA     | AA (   | binary | /) of th | ne disj | olay o | lata R  | AM is  | s set in | n the c | lisplay start |

| at the top of | of the s | creen  | Figu   | re 1 sh  | owse    | xamj   | ples of | displ  | ay(1/    | 64 dut  | y cycle) wh   |

| the displa    | y duty   | cycle  | is 1/6 | 64 or 1  | nore (  | ex. 1  | /32, 1  | /24 e  | tc.), tl | he dat  | a of total li |

| from the l    | ine sp   | ecifie | d by d | lisplay  | y start | line   | instru  | ction, | is di    | splaye  | ed.           |

| See figure    | 1.       |        |        |          |         |        |         |        |          |         |               |

|               |          |        |        |          |         |        |         |        |          |         |               |

| Set page (    | X add    | lress) |        |          |         |        |         |        |          |         |               |

line register and displayed en the start line=0-3. When ne number of LCD screen,

#### page

| R/W D/IDB7 |   |   |   |   | D | <b>B</b> 0 |   |   |   |   |

|------------|---|---|---|---|---|------------|---|---|---|---|

| Code       | 0 | 0 | 1 | 0 | 1 | 1          | 1 | А | А | Α |

| MSBLSB     |   |   |   |   |   |            |   |   |   |   |

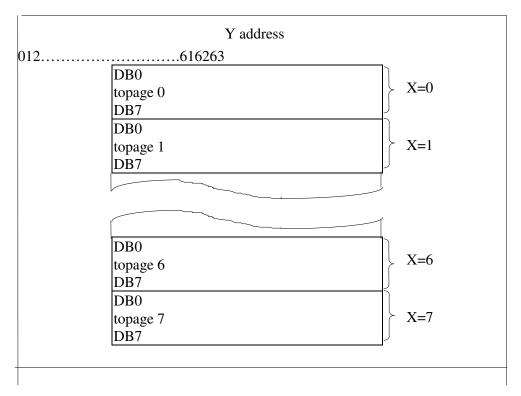

X address AAA (binary) of the display data RAM is set in the X address register. After that, writing or reading to or from MPU is executed in this specified page until the next page is set. See figure 2.

#### Set Y Address

| R/W D/IDB7 |   |   |   |   | D | <b>B</b> 0 |   |   |   |   |

|------------|---|---|---|---|---|------------|---|---|---|---|

| Code       | 0 | 0 | 0 | 1 | А | А          | А | А | А | Α |

| MSBLSB     |   |   |   |   |   |            |   |   |   |   |

Y address AAAAAA (binary) of the display data RAM is set in the Y address Counter. After that, Y address counter is increased by 1 every time the data is written or read to or from MPU.

#### **Status Read**

| R/WD/IDB7 |                 |  |  | DB0 |  |      |   |   |   |   |  |  |

|-----------|-----------------|--|--|-----|--|------|---|---|---|---|--|--|

| Code      | Code 1 0 BUSY 0 |  |  |     |  | REST | 0 | 0 | 0 | 0 |  |  |

| MSBLS     |                 |  |  |     |  |      |   |   |   |   |  |  |

• Busy

When busy is 1, the LSI is executing internal operations. No instructions are accepted while busy is 1, so you should make sure that busy is 0 before writing the next instruction.

#### • ON/OFF

Shows the liquid crystal display conditions: on condition or off condition.

When on/off is 1, the display is in off condition. When on/off is 0, the display is in on condition.

#### • RESET

RESET=1 shows that the system is being initialized. In this condition, no instructions except status read can be accepted.

RESET=0 shows that initializing has finished and the system is in the usual operation condition.

#### Write Display Data

| R/W D/IDB7 | ••••• |   |   |   | ] | DB0 |   |   |   |   |

|------------|-------|---|---|---|---|-----|---|---|---|---|

| Code       | 0     | 1 | D | D | D | D   | D | D | D | D |

|            |       |   |   |   |   |     |   |   |   |   |

MSBLSB

Write 8-bit data DDDDDDDD (binary) into the display data RAM. Then Y address is increased by 1 automatically.

#### **Read Display Data**

| R/W D/IDB7 | ••••• |   |   |   | 1 | DB0 |   |   |   |   |

|------------|-------|---|---|---|---|-----|---|---|---|---|

| Code       | 1     | 1 | D | D | D | D   | D | D | D | D |

|            |       |   |   |   |   |     |   |   |   |   |

MSBLSB

Reads out 8-bit data DDDDDDDD (binary) from the display data RAM. Then Y address is increased by 1 automatically.

One dummy read is necessary right after the address setting. For details, refer to the explanation of output register in "Function of Each Block".

POWERTIP TECHNOLOGY CORPORATION

Display devices for better electronic design

Figure 2 Address Configuration of Display Data RAM

Note: "128\*64" consist of 2 "64\*64"

$CS1 \Rightarrow$  Chip enable for left 64\*64 (segment1 to segment 64)

$CS2 \Rightarrow$  Chip enable for right 64\*64 (segment 65 to segment 128)