### **TO-263AB (D2PAK)**

#### **On-State Current**

**Gate Trigger Current**

16 Amp

≤ 10 mA

#### Off-State Voltage

400 V ÷ 800 V

#### **FEATURES**

- Glass/passivated die junctions

- Medium current Triac

- Ideal for automated placement

- Low thermal resistance

- High surge current capability

- Low forward voltage drop

- Solder dip 260°C, 10s

- Component in accordance to RoHS 2011/65/EU and WEEE 2002/96/EC

- Meets MSL level 3, per J-STD-020, LF maximum peak of 260° C

#### **MECHANICAL DATA**

- Case: TO-263AB (D2PAK). Epoxy meets UL 94V-0 flammability rating.

- **Polarity:** As marked on the body.

- **Terminals:** Matte tin plated leads, solderable per MIL-STD-750 Method 2026, J-STD-002 and JESD22-B102. Consumer grade, meets JESD 201 class 1A whisker test.

#### TYPICAL APPLICATIONS

Logic level versions are designed to interface directly with low power drivers such as microcontrollers.

## Maximun Ratings and Electrical Characteristics at 25°C

| SYMBOL              | PARAMETER                                 | CONDITIONS                                  | Value      | Unit             |

|---------------------|-------------------------------------------|---------------------------------------------|------------|------------------|

| I <sub>T(RMS)</sub> | RMS On-state Current (full sine wave)     | All Conduction Angle, T <sub>c</sub> =95 °C | 16         | А                |

| I <sub>TSM</sub>    | Non-repetitive On-State Current           | Full Cycle, 60 Hz (t = 16.7 ms)             | 176        | А                |

| I <sub>TSM</sub>    | Non-repetitive On-State Current           | Full Cycle, 50 Hz (t = 20 ms)               | 160        | А                |

| I <sup>2</sup> t    | Fusing Current                            | tp = 10 ms, Half Cycle                      | 128        | A <sup>2</sup> s |

| I <sub>GM</sub>     | Peak Gate Current                         | 20 μs max. Tj = 125 °C                      | 4          | А                |

| $P_{G(AV)}$         | Average Gate Power Dissipation            | Tj = 125 °C                                 | 1          | W                |

| dI/dt               | Critical rate of rise of on-state current | $I_G = 2x I_{GT}, t_r \le 100 \text{ns}$    | 50         | A/µs             |

|                     |                                           | f = 120 Hz, T <sub>j</sub> = 125 °C         |            |                  |

| T <sub>j</sub>      | Operating Temperature                     |                                             | (-40 +125) | °C               |

| T <sub>stg</sub>    | Storage Temperature                       |                                             | (-40 +150) | °C               |

| T <sub>sld</sub>    | Soldering Temperature                     | 10s max                                     | 260        | °C               |

| SYMBOL            | PARAMETER                         | VOLTAGE |     |     | Unit |

|-------------------|-----------------------------------|---------|-----|-----|------|

| OTIVIBUL          |                                   | D       | M   | N   |      |

| $V_{DRM}/V_{RRM}$ | Repetitive Peak Off State Voltage | 400     | 600 | 800 | V    |

Revision: 1

## Electrical Characteristics at Tamb = 25 °C

| SYMBOL PARAMETER                   |                                        | CONDITIONS                                                                     | Quadrant |     | SENSITIVITY |      | I loit     |

|------------------------------------|----------------------------------------|--------------------------------------------------------------------------------|----------|-----|-------------|------|------------|

| SYMBOL                             | PARAMETER                              | CONDITIONS                                                                     | Quadrant |     | 08          | 09   | Unit       |

| I <sub>GT</sub> <sup>(1)</sup>     | Gate Trigger Current                   | $V_D = 12 V_{DC}, R_L = 33 \ \Omega,  T_j = 25 \ ^{\circ}C$                    | Q1÷Q3    | MAX | 10          | 10   | mA         |

|                                    |                                        |                                                                                | Q4       | MAX | -           | 10   | mA         |

| V <sub>GT</sub>                    | Gate Trigger Voltage                   | $V_D = 12V_{DC}, R_L = 33\;\Omega, T_j = 25\;{}^{\circ}C$                      | Q1÷Q3    | MAX | 1.2         | 1.3  | V          |

|                                    |                                        |                                                                                | Q1÷Q4    | MAX |             | 1.3  | V          |

| $V_{GD}$                           | Gate Non Trigger Voltage               | $V_D = V_{DRM}, R_L = 3.3\; K\Omega,\; T_j = 125\; ^{\circ}C$                  | Q1÷Q3    | MIN | 0.2         | 0.2  | V          |

|                                    |                                        |                                                                                | Q1÷Q4    | MIN |             | 0.2  | V          |

| I <sub>H</sub> (2)                 | Holding Current                        | $I_T = 100 \text{ mA}$ , Gate open, $T_j = 25 \text{ °C}$                      |          | MAX | 15          | 20   | mA         |

| IL                                 | Latching Current                       | $I_G = 1.2 I_{GT}, T_j = 25 \degree C$                                         | Q1,Q3    | MAX | 25          |      | mA         |

|                                    |                                        |                                                                                | Q1,Q3,Q4 | MAX |             | 20   | mA         |

|                                    |                                        |                                                                                | Q2       | MAX | 30          | 25   | mA         |

| dV/dt (2)                          | Critical Rate of Voltage Rise          | $V_D = 0.67 \times V_{DRM}$ , Gate open                                        |          | MIN | 40          | 40   | V/µs       |

|                                    |                                        | $T_j = 125  ^{\circ}\text{C}$                                                  |          |     |             |      |            |

| (dl/dt)c (2)                       | Critical Rate of Current Rise          | $(dv/dt)c = 0.1 V/\mu s$ $T_j = 125 °C$                                        |          | MIN | 8.5         | 2.5  | A/ms       |

|                                    |                                        | $(dv/dt)c = 10 V/\mu s$ $T_j = 125 °C$                                         |          | MIN | 3.0         | 1.5  | A/ms       |

|                                    |                                        | without snubber $T_j = 125$ °C                                                 |          | MIN | -           | -    |            |

| V <sub>TM</sub> (2)                | On-state Voltage                       | $I_T = 22.5 \text{ Amp, tp} = 380 \ \mu\text{s, } T_j = 25 \ ^{\circ}\text{C}$ |          | MAX | 1.6         | 1.6  | V          |

| V <sub>to</sub> (2)                | Threshold Voltage                      | $T_j = 125  ^{\circ}\text{C}$                                                  |          | MAX | 0.85        | 0.77 | V          |

| r <sub>d</sub> <sup>(2)</sup>      | Dynamic resistance                     | $T_j = 125 ^{\circ}\text{C}$                                                   |          | MAX | 25          | 50   | m $\Omega$ |

| I <sub>DRM</sub> /I <sub>RRM</sub> | Off-State Leakage Current              | $V_D = V_{DRM}$ , $T_j = 125 °C$                                               |          | MAX | 2           | 2    | mA         |

|                                    |                                        | $V_R = V_{RRM}$ , $T_j = 25$ °C                                                |          | MAX | Ę           | 5    | μΑ         |

| R <sub>th(j-c)</sub>               | Thermal Resistance<br>Junction-Case    | for AC 360° conduction angle                                                   |          |     | 1           | .1   | °C/W       |

| R <sub>th(j-a)</sub>               | Thermal Resistance<br>Junction-Ambient | $S = 1 cm^2$                                                                   |          |     | 45          |      | °C/W       |

<sup>(1)</sup> Minimum I<sub>GT</sub> is guaranted at 5% of I<sub>GT</sub> max.

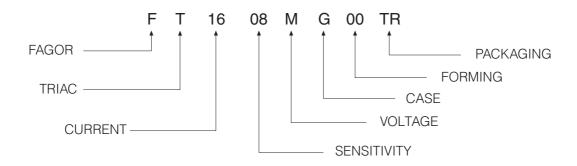

#### **Part Number Information**

Revision: 1

<sup>(2)</sup> For either polarity of electrode MT2 voltage with reference to electrode MT1.

## **Ordering information**

| PREFERRED P/N | PACKAGE CODE | DELIVERY MODE              | BASE QUANTITY | UNIT WEIGHT (g) |

|---------------|--------------|----------------------------|---------------|-----------------|

| FT1609MG 00TR | TR           | 13" diameter tape and reel | 800           | 1.50            |

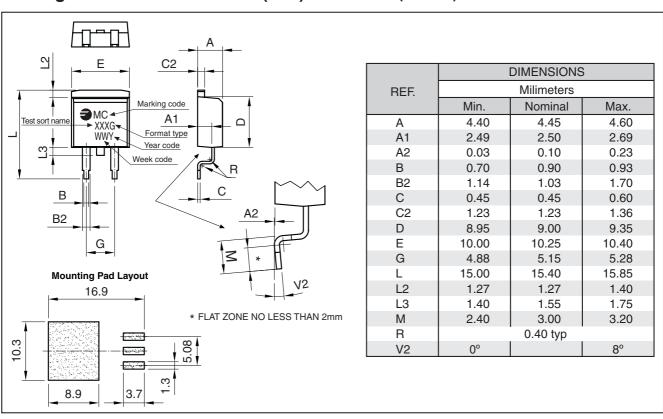

# Package Outline Dimensions: (mm) TO-263AB (D2PAK)

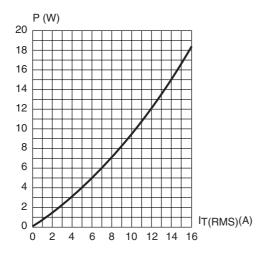

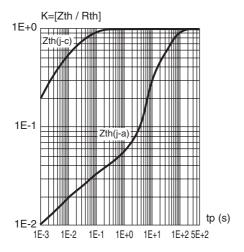

# Ratings and Characteristics (Ta 25 °C unless otherwise noted)

Fig. 1: Maximum power dissipation versus RMS on-state current (full cycle)

Fig. 3: Relative variation of thermal impedance versus pulse duration.

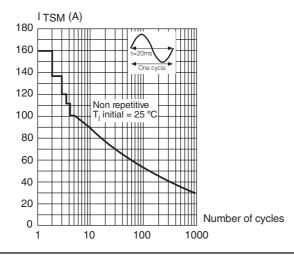

Fig. 5: Surge peak on-state current versus number of cycles

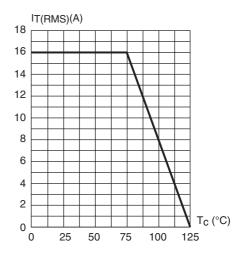

Fig. 2: RMS on-state current versus case temperature (full cycle).

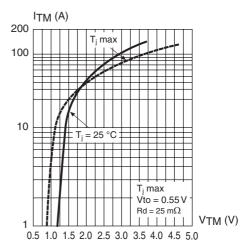

Fig. 4: On-state characteristics (maximum values)

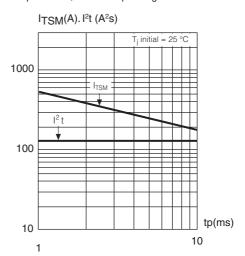

Fig. 6: Non repetitive surge peak on-state current for a sinusoidal pulse with width: tp < 10 ms, and corresponding value of I<sup>2</sup>t.

# Ratings and Characteristics (Ta 25 °C unless otherwise noted)

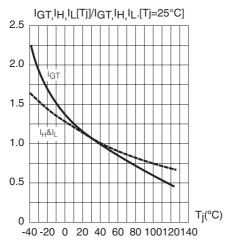

Fig. 7: Relative variation of gate trigger current, holding current and latching versus junction temperature (typical values)

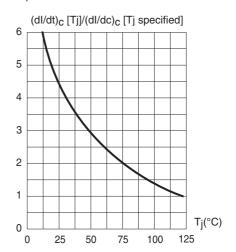

Fig. 9: Relative variation of critical rate of decrease of main current versus

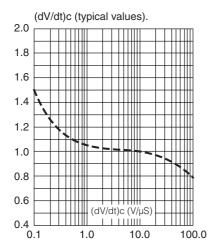

Fig. 8: Relative variation of critical rate of decrease of main current versus junction temperature

### **Revision History**

| Date        | Revision | Description of Changes                       |

|-------------|----------|----------------------------------------------|

| 12-Oct-2004 | 0        | Original Data Sheet                          |

| 10-Oct-2013 | 1        | 200V and 700V eliminated, Add Sensitivity 08 |

### **Disclaimer**

All product, product specifications and data are subject to change without notice to improve reliability, function or design or otherwise.

Fagor Electrónica, S.Coop., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Fagor"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Fagor makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Fagor disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Fagor's knowledge of typical requirements that are often placed on Fagor products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Fagor's terms and conditions of purchase, including but nos limited to the warranty expressed therein.

Except as expressly indicated in writing. Fagor products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Fagor product could result in personal injury or death. Customers using or selling Fagor products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Fagor and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attomeys fees, even if such claim alleges that Fagor or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Fagor personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Fagor, Product names and markings noted herein may be trademarks of their respective owners.

Revision: 1